EE 101 Lecture 10, Feb 12, 2019

Ruiz 4 Avg = 7.22

$$\alpha = 1.97$$

Midterm Avg = 73.96

(101 students)  $\alpha = 16.00$

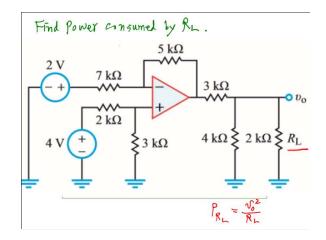

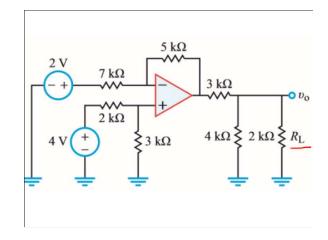

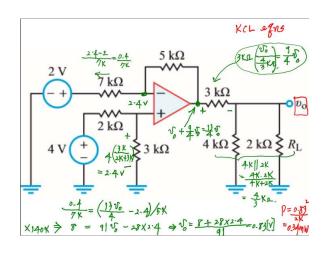

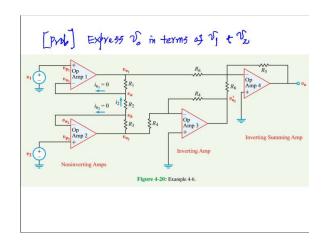

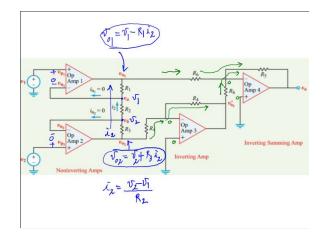

Since

$$i_{n_1}=i_{n_2}=0$$

(op-amp current constraint),

$$i_2=\frac{v_0-v_0}{R_2}=\frac{v_2-v_1}{R_2}\;,$$

and

$$v_{v_2}-v_{v_1}=i_2(R_1+R_2+R_3)\\ =\left(\frac{R_1+R_2+R_3}{R_2}\right)(v_2-v_1). \tag{4.50}$$

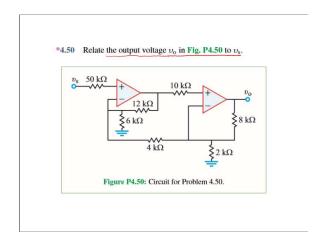

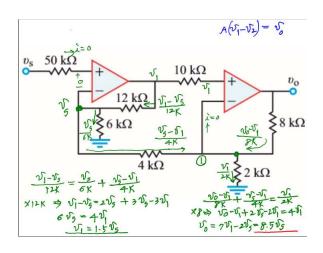

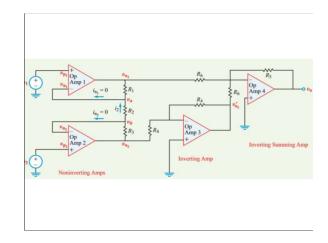

Op amp 3 is a standard inverting amplifier, so we can use Table 4-3(c) to obtain

$$v'_{v_2}=-\left(\frac{R_4}{R_4}\right)v_{v_2}=-v_{v_2}.$$

Op amp 4 is an inverting summing amplifier (Table 4-3(c)) with output

$$u_0=-\frac{R_3}{R_6}(v_{v_1}+v'_{v_2})\\ =-\frac{R_3}{R_6}(v_{v_2}-v_{v_1})=R_3\left(\frac{R_1+R_2+R_3}{R_6R_2}\right)(v_2-v_1). \tag{4.51}$$

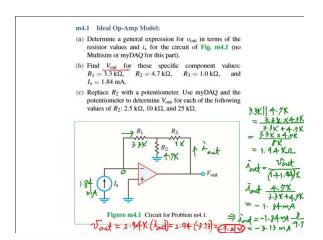

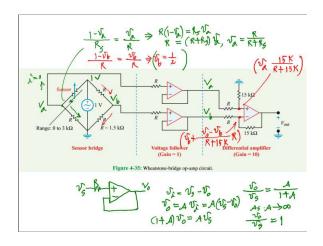

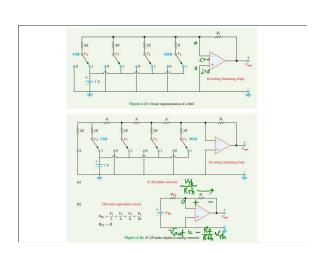

A

$$V_{K}$$

$\frac{15K}{15K+R}$   $-(V_{b} + \frac{V_{b}-V_{b}}{K+15K}R) = V_{o}$

$V_{K}$

$V_$

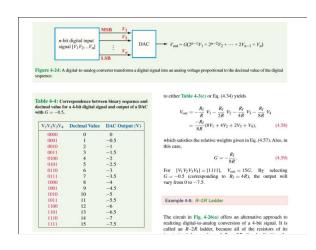

#### 4-10 Digital-to-Analog Converters (DAC)

➤ A digital-to-analog converter (DAC) is a circuit that transforms a digital sequence presented to its input into an analog output voltage whose magnitude is proportional to the decimal value of the input signal.

the decimal value of the input signal. ◀

An *n*-bit digital signal is described by the sequence [V<sub>1</sub>V<sub>2</sub>V<sub>3</sub>...V<sub>4</sub>], where V<sub>1</sub> is called the *most significant bit* (MSB) and V<sub>6</sub> is the *least significant bit* (MSB) and V<sub>6</sub> is the *least significant bit* (LSB). Voltages V<sub>1</sub> through V<sub>6</sub> can each assume only two possible states—either a0 or a 1. When a bit is in the 1 state, its decimal value is 2<sup>n</sup>, where *m* depends on the location of that bit in the sequence. For the most significant bit (V<sub>1</sub>), its decimal value is 2<sup>n-1</sup>); for V<sub>2</sub> it is 2<sup>n-2</sup>); and so on. The decimal value of the least significant bit is 2<sup>n-2</sup> = 2<sup>0</sup> = 1, when that bit is in state 1. Any bit in state 0 has a decimal value of 0. Table 4-# illustrates the correspondence between the binary sequences star at lof0000 and end at [1111], representing 16 decimal values extending from 0 to 15 and inclusive of both ends. To do so, the DAC in Fig. 4-24 has to sum V<sub>1</sub> to V<sub>n</sub> after weighting each by a factor equal to its decimal value. Thus, for a 4-bit digital sequence, for example, the output voltage of the DAC has to be related to the input by V<sub>0</sub> at = G(2<sup>d-1</sup>V<sub>1</sub> + 2<sup>d-2</sup>V<sub>2</sub> + 2<sup>d-3</sup>V<sub>3</sub> + 2<sup>d-4</sup>V<sub>4</sub>)

= G(8V<sub>1</sub> + 4V<sub>2</sub> + 2V<sub>3</sub> + V<sub>4</sub>). (4.57)

$$= G(2 - V_1 + 2 - V_2 + 2 - V_3 + 2 - V_4)$$

$$= G(8V_1 + 4V_2 + 2V_3 + V_4), \tag{4.5}$$

# First Successful Operation of MOS Transistor

Dawon Kahng (May 4, 1931- May 13, 1992)

Dr. Kahng, with M. Atalla, fabricated a MOSFET using a gate insulator formed from high quality SiO2 grown by a new high-pressure steam oxidation process at Bell Labs (1960)

Invented in 1967 a field effect memory, the first nonvolatile silicon memory (floating gate memory)

Simon Sze

1

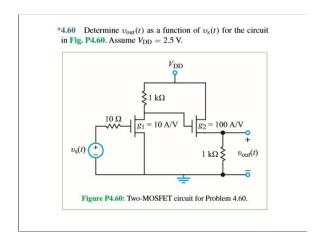

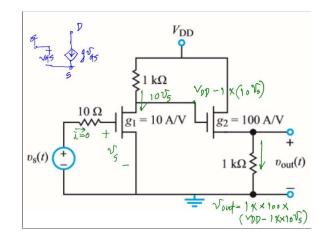

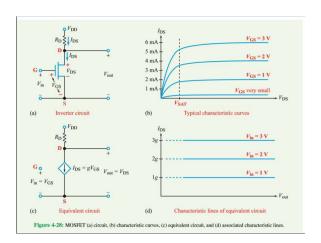

## 4-11 The MOSFET as a Voltage-Controlled Current Source

In earlier sections, we demonstrated how op amps can be used to build buffers and amplifiers. We now examine how to realize the same outcome using MOSFETs. The simplest model of a MOSFET, which stands for metal-oxide semiconductor field-effect transistor, is shown in Fig. 4-27(a). The vast majority of commercial computer processors are built with MOSFETs, as mentioned in Technology Brief 1 on nanotechnology, a 2010 Intel Core processor contains over 1 billion independent MOSFETs. A MOSFET has three terminals: the gate (G), the source (S), and the drain (D). Actually, it has a fourth terminal, namely its body (B), but we will ignore it for now because for many applications it is simply connected to the ground terminal. The circuit symbol for the MOSFET may look somewhat unusual, but it is actually a stylized depiction of the physical cross section of a real MOSFET. In a real MOSFET, the gate

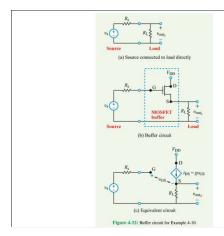

#### (b) With MOSFET Buffer

For the circuit in Fig. 4-32(c), in which the MOSFET has been replaced with its equivalent circuit, KVL gives

$$-\upsilon_{s}+\upsilon_{GS}+\upsilon_{out_{2}}=0.$$

Also,

$$\begin{split} \nu_{\text{out}_2} &= I_{\text{DS}} R_{\text{L}} \\ &= g R_{\text{L}} \nu_{\text{GS}}. \ \, \equiv \ \, \text{g R}_{\text{L}} \left( \text{V}_{\text{g}} - \text{V}_{\text{out}_{\text{2}}} \right) \end{split}$$

Simultaneous solution of the two equations gives

$$\Rightarrow \quad v_{\text{out}_2} = \left(\frac{gR_{\text{L}}}{1 + gR_{\text{L}}}\right)v_8.$$

With  $g=10\,{\rm A/V}$  and in order for  $\upsilon_{{\rm out}_2}$  to be no less than  $0.99\upsilon_{\rm s}$ , it is necessary that

$$R_{\rm L} \geq 9.9 \, \Omega$$

which is three orders of magnitude smaller than the requirement for the unbuffered circuit.

### Section 4-11: MOSFET

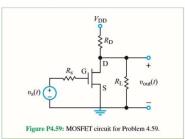

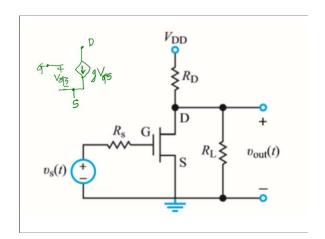

4.59 In Example 4-9, we analyzed a common-source amplifier without a load resistance. Consider the amplifier in Fig. P4.59; it is identical to the circuit in Fig. 4-31, except that we have added a load resistor  $R_{\rm L}$ . Obtain an expression for  $\upsilon_{\rm out}$  as a function of  $\upsilon_{\rm s}$ .